JTAG (Grupo de acción de prueba conjunta) es un protocolo ampliamente utilizado para la depuración, programación y prueba de circuitos integrados (ICS). Permite la comunicación directa con un chip para leer su memoria, realizar escaneos de límites o cargar firmware. Este tutorial lo guiará a través de los conceptos básicos de usar JTAG para leer chips, incluida la configuración, las herramientas y las mejores prácticas.

¿Qué es JTAG?

JTAG es una interfaz estandarizada (IEEE 1149.1) que proporciona una forma de probar y depurar hardware a nivel de chip. Se usa comúnmente en:

- Desarrollo y depuración de firmware

- Prueba de conexiones de PCB

- Firmado intermitente en dispositivos

- Extraer memoria de ICS

JTAG usa una interfaz de 4 o 5 pines:

| Alfiler | Descripción |

|---|---|

| TDI | Probar datos en |

| TDO | Probar datos |

| TCK | Reloj de prueba |

| TMS | Modo de prueba Seleccionar |

| Trst | Restablecer de prueba (opcional) |

Lo que necesitarás

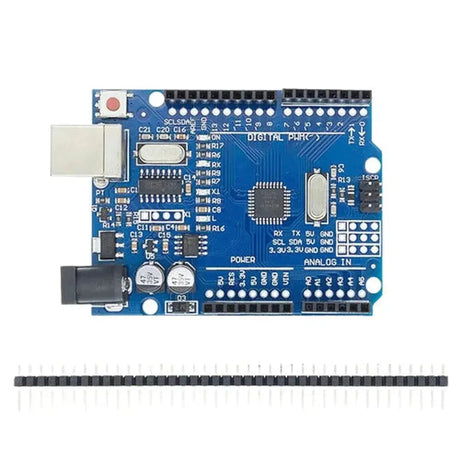

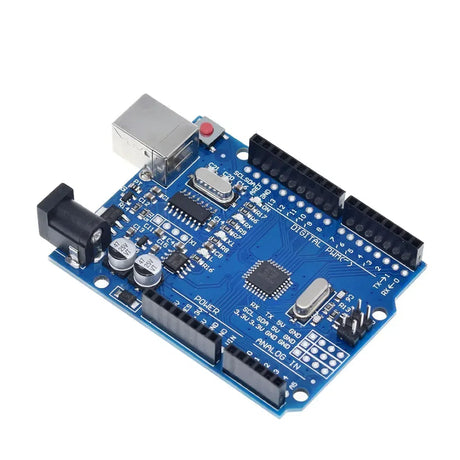

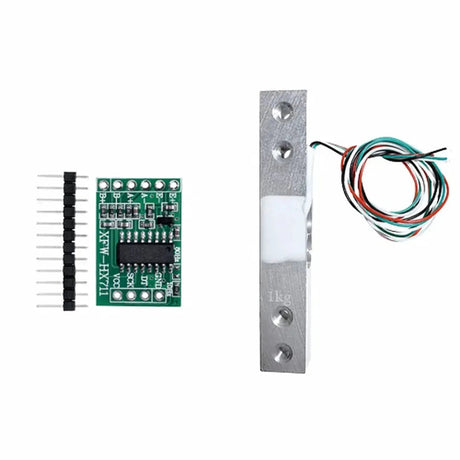

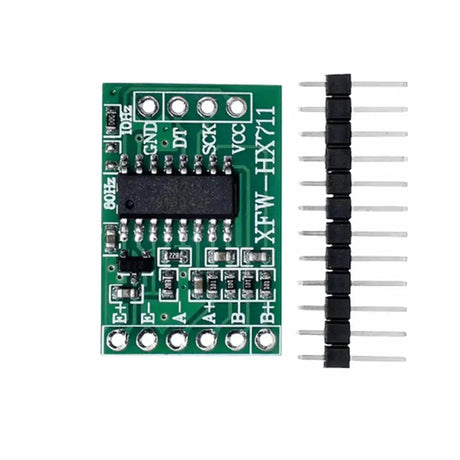

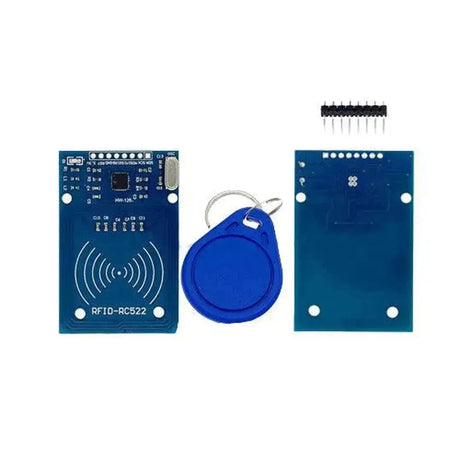

- Adaptador JTAG: Un dispositivo de hardware para interactuar con el chip (por ejemplo, Segger J-Link, adaptadores respaldados por OpenOCD).

- Dispositivo objetivo: El IC o el sistema que desea leer.

- Herramientas de software: Aplicaciones para la depuración de JTAG, como OpenOCD, Urjtag o herramientas propietarias.

- Documentación de JTAG Pinout: Diagrama de Pinout para el dispositivo de destino.

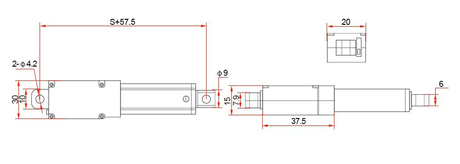

- Accesorios de conexión: Cables, encabezados y una placa (si es necesario).

Paso 1: Configuración del hardware JTAG

1. Identifique la interfaz JTAG en el dispositivo de destino

- Consulte la hoja de datos del chip o los esquemas de PCB para localizar los pines JTAG.

- Las etiquetas comunes para los pasadores JTAG incluyen

TDI,TDO,TCK, yTMS. - Algunos tableros han etiquetado con los encabezados JTAG (por ejemplo, conectores de 10 pines o 20 pines).

2. Conecte el adaptador JTAG

- Cablee el adaptador con el dispositivo de destino, coincidiendo con JTAG PINOUT:

-

TDIen el adaptador se conecta aTDIen el dispositivo, y así sucesivamente. - Asegúrese de que GND esté conectado entre el adaptador y el objetivo.

- Proporcione energía al dispositivo de destino si es necesario.

-

3. Verifique los niveles de voltaje

- Asegúrese de que el adaptador JTAG admite los niveles de voltaje del dispositivo objetivo (por ejemplo, 3.3V o 1.8V).

- Algunos adaptadores tienen configuraciones de voltaje configurables.

Paso 2: Instalación de herramientas de software JTAG

1. OpenOCD (Open On Chip Depugger)

OpenOCD es una herramienta de código abierto ampliamente utilizada para la depuración de JTAG.

- Instálelo con su administrador de paquetes (por ejemplo,

apt install openocden Linux). - Asegúrese de que su adaptador JTAG sea compatible con OpenOCD.

2. Urjtag

Una herramienta liviana para el escaneo límite y las operaciones básicas de JTAG.

- Instalación a través de Sitio web de Urjtag.

3. Herramientas específicas del proveedor

Para adaptadores patentados como Segger J-Link o Xilinx, use su software oficial:

- Segger J-Link: Descargue las herramientas J-Link desde Sitio web de Segger.

- Xilinx Herramientas: Use Vivado o Impact para la depuración de FPGA.

Paso 3: Leer datos de un chip

1. Configure el software JTAG

- Cree o cargue un archivo de configuración que especifique el adaptador JTAG y el dispositivo de destino.

- Ejemplo para OpenOCD:

source [find interface/jlink.cfg] transport select jtag source [find target/stm32f4x.cfg] init halt

- Ejemplo para OpenOCD:

2. Detectar el dispositivo objetivo

Ejecute un comando para escanear la cadena JTAG e identificar dispositivos conectados.

- Para OpenOcd:

Busque dispositivos detectados en el registro de salida.openocd -f interface/jlink.cfg -f target/stm32f4x.cfg

3. Contenido de la memoria de volcado

Use comandos JTAG para leer regiones de memoria:

- Para OpenOcd:

dump_image memory.bin 0x08000000 0x10000-

memory.bin: Archivo para guardar el volcado de memoria. -

0x08000000: Iniciar dirección. -

0x10000: Número de bytes para leer.

-

4. Realizar escaneos límite

Los escaneos límite verifican la conectividad y la funcionalidad de los pines IC.

- Use Urjtag o OpenOCD para realizar escaneos límite.

- Ejemplo en Urjtag:

cable jtagkey detect bsdl path/to/bsdl/file.bsd svf boundary_scan.svf

Paso 4: Mejores prácticas para la depuración de JTAG

- Asegure la conexión: Use cables cortos y confiables para minimizar el ruido.

- Verifique Pinout: Verifique dos veces las conexiones del pin JTAG para evitar dañar el dispositivo.

- Firmware de copia de seguridad: Siempre haga una copia de seguridad del firmware original antes de hacer cambios.

- Use el software correcto: Asegúrese de que la herramienta que esté utilizando admite el dispositivo de destino.

- Voltaje de monitor: Asegúrese de que el dispositivo de destino funcione al nivel de voltaje correcto.

Aplicaciones de JTAG

- Depuración de firmware y software

- Flasheando nuevo firmware o cargadores de arranque

- Extraer datos de la memoria para el análisis

- Diagnóstico de defectos de fabricación de PCB

- Hardware de ingeniería inversa

Solución de problemas

-

Dispositivo no detectado:

- Verifique el cableado y el pinout.

- Asegúrese de que el dispositivo de destino esté encendido.

- Verifique los niveles de voltaje para la compatibilidad.

-

Errores JTAG:

- Asegúrese de que se utilice el archivo de configuración correcto.

- Intente reducir la velocidad del reloj JTAG si falla la comunicación.

-

Problemas de permiso:

- En Linux, asegúrese de tener los permisos adecuados para acceder a dispositivos USB (use

sudoo configurarudevnormas).

- En Linux, asegúrese de tener los permisos adecuados para acceder a dispositivos USB (use

Conclusión

JTAG es una herramienta invaluable para depurar y programar chips a un nivel bajo. Al comprender los conceptos básicos del hardware y el software JTAG, puede leer la memoria de chips, depurar firmware y realizar escaneos de límites. ¡Experimente con diferentes herramientas y configuraciones para utilizar completamente JTAG en sus proyectos!