Ang JTAG (Joint Test Action Group) ay isang malawak na ginagamit na protocol para sa pag -debug, programming, at pagsubok ng integrated circuit (ICS). Pinapayagan nito ang direktang komunikasyon sa isang chip na basahin ang memorya nito, magsagawa ng mga hangganan ng pag -scan, o pag -load ng firmware. Ang tutorial na ito ay gagabay sa iyo sa pamamagitan ng mga pangunahing kaalaman sa paggamit ng JTAG upang mabasa ang mga chips, kabilang ang pag -setup, tool, at pinakamahusay na kasanayan.

Ano ang jtag?

Ang JTAG ay isang standardized interface (IEEE 1149.1) na nagbibigay ng isang paraan upang subukan at i -debug ang hardware sa antas ng chip. Ito ay karaniwang ginagamit sa:

- Pag -unlad at pag -debug ng firmware

- Pagsubok sa mga koneksyon sa PCB

- Kumikislap na firmware sa mga aparato

- Pagkuha ng memorya mula sa ICS

Gumagamit si JTAG ng isang 4 o 5-pin interface:

| Pin | Paglalarawan |

|---|---|

| Tdi | Pagsubok ng data sa |

| TDO | Pagsubok ng data |

| Tck | Pagsubok sa orasan |

| TMS | Piliin ang mode ng pagsubok |

| Trst | Pagsubok sa Pagsubok (Opsyonal) |

Ano ang kakailanganin mo

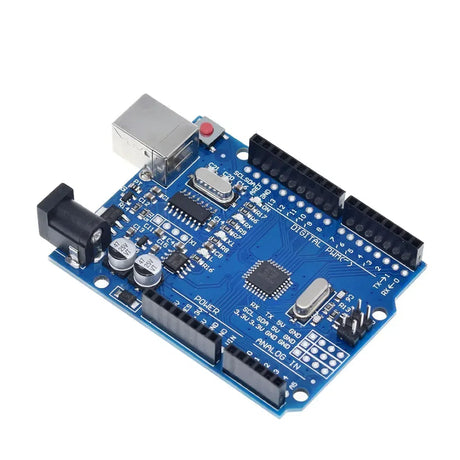

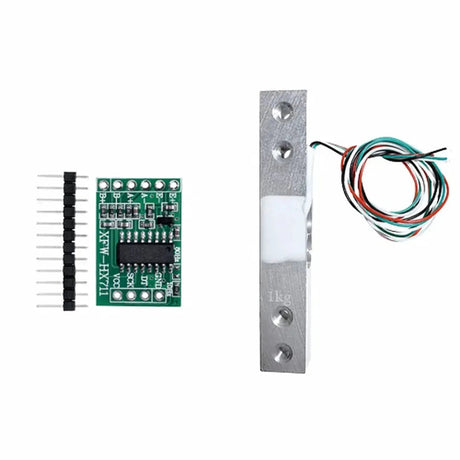

- Jtag adapter: Isang aparato ng hardware upang makipag-ugnay sa chip (hal., Segger J-Link, OpenOCD na suportado ng mga adaptor).

- Target na aparato: Ang IC o system na nais mong basahin.

- Mga tool sa software: Mga aplikasyon para sa pag -debug ng JTAG, tulad ng OpenOCD, URJTAG, o mga tool sa pagmamay -ari.

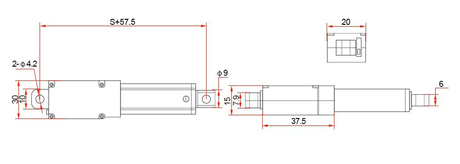

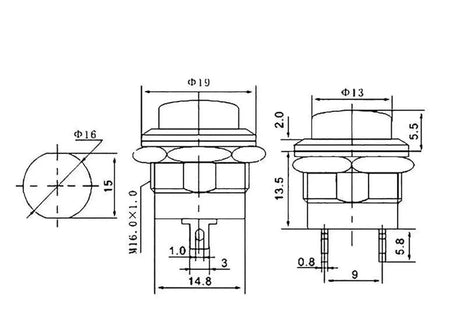

- Dokumentasyon ng JTAG PINOUT: Diagram ng Pinout para sa target na aparato.

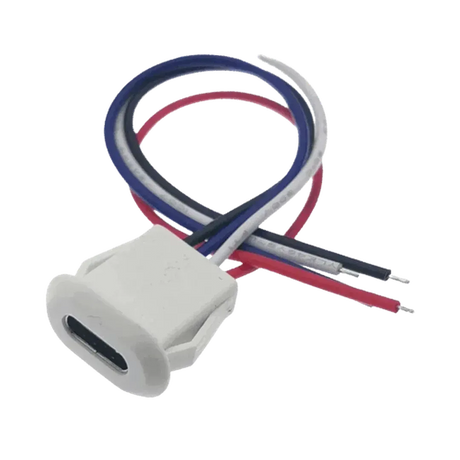

- Mga Kagamitan sa Koneksyon: Mga wire, header, at isang breadboard (kung kinakailangan).

Hakbang 1: Pag -set up ng JTAG hardware

1. Kilalanin ang interface ng JTAG sa target na aparato

- Sumangguni sa Chip's Datasheet o PCB Schematics upang hanapin ang mga JTAG pin.

- Kasama sa mga karaniwang label para sa JTAG pin

TDI,TDO,TCK, atTMS. - Ang ilang mga board ay may label na mga header ng JTAG (hal., 10-pin o 20-pin na konektor).

2. Ikonekta ang JTAG adapter

- I -wire ang adapter sa target na aparato, na tumutugma sa jtag pinout:

-

TDISa adapter ay kumokonekta saTDIsa aparato, at iba pa. - Tiyakin na ang GND ay konektado sa pagitan ng adapter at ang target.

- Magbigay ng kapangyarihan sa target na aparato kung kinakailangan.

-

3. Patunayan ang mga antas ng boltahe

- Tiyakin na sinusuportahan ng adapter ng JTAG ang mga antas ng boltahe ng target na aparato (hal., 3.3V o 1.8V).

- Ang ilang mga adapter ay may mga setting ng boltahe na naka -configure.

Hakbang 2: Pag -install ng mga tool ng software ng JTAG

1. OpenOCD (Buksan ang On-Chip Debugger)

Ang OpenOCD ay isang open-source na tool na malawakang ginagamit para sa pag-debug ng JTAG.

- I -install ito gamit ang iyong manager ng package (hal.

apt install openocdsa Linux). - Tiyakin na ang iyong JTAG adapter ay suportado ng OpenOCD.

2. Urjtag

Isang magaan na tool para sa pag -scan ng hangganan at pangunahing operasyon ng JTAG.

- I -install ang VIA website ng urjtag.

3. Mga tool na partikular sa Vendor

Para sa pagmamay-ari ng mga adaptor tulad ng Segger J-Link o Xilinx, gamitin ang kanilang opisyal na software:

- Segger J-Link: I-download ang mga tool ng J-Link mula sa Website ng Segger.

- Mga tool sa Xilinx: Gumamit ng vivado o epekto para sa pag -debug ng FPGA.

Hakbang 3: Ang pagbabasa ng data mula sa isang chip

1. I -configure ang JTAG software

- Lumikha o mag -load ng isang file ng pagsasaayos na tumutukoy sa JTAG adapter at target na aparato.

- Halimbawa para sa OpenOCD:

source [find interface/jlink.cfg] transport select jtag source [find target/stm32f4x.cfg] init halt

- Halimbawa para sa OpenOCD:

2. Hanapin ang target na aparato

Patakbuhin ang isang utos upang i -scan ang chain ng JTAG at kilalanin ang mga konektadong aparato.

- Para sa OpenOCD:

Maghanap para sa mga napansin na aparato sa log ng output.openocd -f interface/jlink.cfg -f target/stm32f4x.cfg

3. Dump Memory Nilalaman

Gumamit ng mga utos ng JTAG upang mabasa ang mga rehiyon ng memorya:

- Para sa OpenOCD:

dump_image memory.bin 0x08000000 0x10000-

memory.bin: File upang i -save ang memorya ng memorya. -

0x08000000: Start address. -

0x10000: Bilang ng mga byte na basahin.

-

4. Magsagawa ng mga pag -scan sa hangganan

Suriin ang mga pag -scan ng hangganan para sa pagkakakonekta at pag -andar ng mga pin ng IC.

- Gumamit ng URJTAG o OpenOCD upang maisagawa ang mga pag -scan ng hangganan.

- Halimbawa sa Urjtag:

cable jtagkey detect bsdl path/to/bsdl/file.bsd svf boundary_scan.svf

Hakbang 4: Pinakamahusay na kasanayan para sa pag -debug ng JTAG

- I -secure ang koneksyon: Gumamit ng maikli, maaasahang mga wire upang mabawasan ang ingay.

- I -verify ang pinout: I-double-check ang mga koneksyon sa JTAG pin upang maiwasan ang pagkasira ng aparato.

- Backup firmware: Laging i -back up ang orihinal na firmware bago gumawa ng mga pagbabago.

- Gumamit ng tamang software: Tiyakin na ang tool na ginagamit mo ay sumusuporta sa target na aparato.

- Subaybayan ang boltahe: Tiyakin na ang target na aparato ay nagpapatakbo sa tamang antas ng boltahe.

Mga aplikasyon ng jtag

- Pag -debug ng firmware at software

- Kumikislap ng mga bagong firmware o bootloader

- Pagkuha ng data mula sa memorya para sa pagsusuri

- Pag -diagnose ng mga depekto sa pagmamanupaktura ng PCB

- Reverse engineering hardware

Pag -aayos

-

Hindi nakita ang aparato:

- Patunayan ang mga kable at pinout.

- Tiyakin na ang target na aparato ay pinapagana.

- Suriin ang mga antas ng boltahe para sa pagiging tugma.

-

Mga error sa jtag:

- Tiyaking ginagamit ang tamang file ng pagsasaayos.

- Subukan ang pagbaba ng bilis ng orasan ng JTAG kung nabigo ang komunikasyon.

-

Mga isyu sa pahintulot:

- Sa Linux, tiyakin na mayroon kang wastong mga pahintulot upang ma -access ang mga aparato sa USB (gamitin

sudoo i -configureudevmga patakaran).

- Sa Linux, tiyakin na mayroon kang wastong mga pahintulot upang ma -access ang mga aparato sa USB (gamitin

Konklusyon

Ang JTAG ay isang napakahalagang tool para sa pag -debug at programming chips sa isang mababang antas. Sa pamamagitan ng pag -unawa sa mga pangunahing kaalaman ng JTAG hardware at software, maaari mong basahin ang memorya ng chip, debug firmware, at magsagawa ng mga pag -scan ng hangganan. Eksperimento sa iba't ibang mga tool at pagsasaayos upang ganap na magamit ang JTAG sa iyong mga proyekto!