JTAG (Joint Test Action Group) est un protocole largement utilisé pour le débogage, la programmation et le test des circuits intégrés (CI). Il permet une communication directe avec une puce pour lire sa mémoire, effectuer des analyses de limite ou charger le firmware. Ce tutoriel vous guidera à travers les bases de l'utilisation de JTAG pour lire des puces, y compris la configuration, les outils et les meilleures pratiques.

Qu'est-ce que JTAG?

JTAG est une interface standardisée (IEEE 1149.1) qui fournit un moyen de tester et de déboguer le matériel au niveau de la puce. Il est couramment utilisé dans:

- Développement et débogage du micrologiciel

- Tester les connexions PCB

- Firmware clignotant sur les appareils

- Extraction de la mémoire de l'ICS

JTAG utilise une interface de 4 ou 5 broches:

| Épingle | Description |

|---|---|

| TDI | Tester les données dans |

| To | Tester les données |

| Tck | Horloge de test |

| TMS | Sélection du mode de test |

| TRST | Test réinitialisation (facultatif) |

Ce dont vous aurez besoin

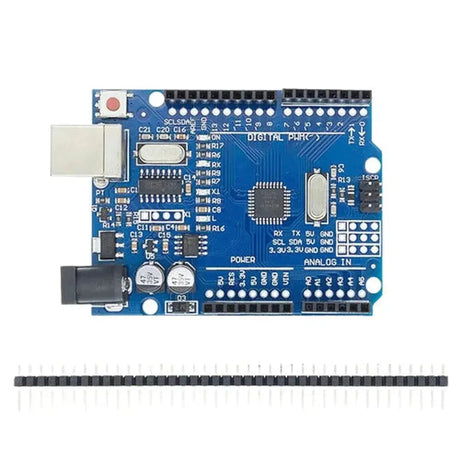

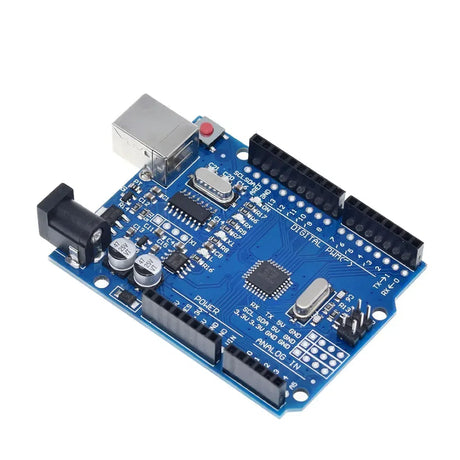

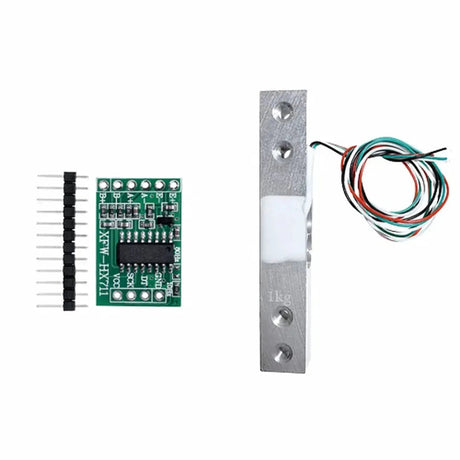

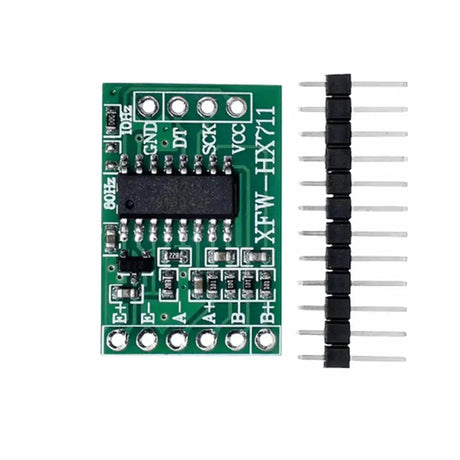

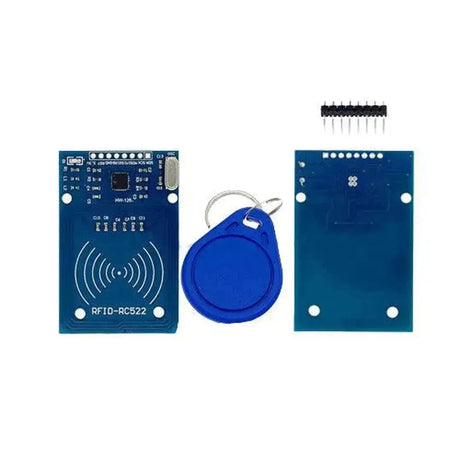

- Adaptateur JTAG: Un périphérique matériel à interface avec la puce (par exemple, SEGGER J-LINK, ADAPTATEURS SUPPORTÉS OpenOCD).

- Dispositif cible: Le CI ou le système que vous souhaitez lire.

- Outils logiciels: Applications pour le débogage de JTAG, telles que OpenOCD, URJTAG ou outils propriétaires.

- Documentation JTAG Pinout: Diagramme Pinout pour le dispositif cible.

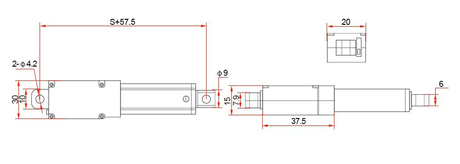

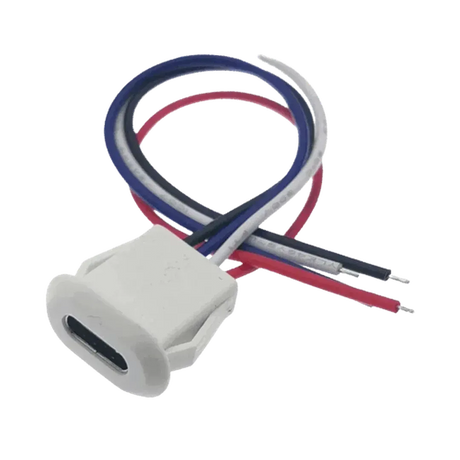

- Accessoires de connexion: Fils, en-têtes et planche à pain (si nécessaire).

Étape 1: Configuration du matériel JTAG

1. Identifiez l'interface JTAG sur le périphérique cible

- Reportez-vous à la fiche technique de la puce ou aux schémas PCB pour localiser les broches JTAG.

- Les étiquettes communes pour les broches JTAG comprennent

TDI,TDO,TCK, etTMS. - Certaines planches ont étiqueté des en-têtes JTAG (par exemple, des connecteurs à 10 broches ou 20 broches).

2. Connectez l'adaptateur JTAG

- Tirez l'adaptateur au périphérique cible, correspondant à la broche JTAG:

-

TDIsur l'adaptateur se connecte àTDIsur l'appareil, etc. - Assurez-vous que GND est connecté entre l'adaptateur et la cible.

- Fournissez de la puissance à l'appareil cible si nécessaire.

-

3. Vérifiez les niveaux de tension

- Assurez-vous que l'adaptateur JTAG prend en charge les niveaux de tension du dispositif cible (par exemple, 3,3 V ou 1,8 V).

- Certains adaptateurs ont des paramètres de tension configurables.

Étape 2: Installation des outils logiciels JTAG

1. OpenOCD (débogueur ouvert sur puce)

OpenOCD est un outil open source largement utilisé pour le débogage de JTAG.

- Installez-le à l'aide de votre gestionnaire de packages (par exemple,

apt install openocdsur Linux). - Assurez-vous que votre adaptateur JTAG est pris en charge par OpenOCD.

2. Urjtag

Un outil léger pour la numérisation des limites et les opérations JTAG de base.

- Installer via Site Web d'Urjtag.

3. Outils spécifiques aux vendeurs

Pour les adaptateurs propriétaires comme Segger J-Link ou Xilinx, utilisez leur logiciel officiel:

- Segger J-Link: Téléchargez les outils J-Link depuis Site Web de Segger.

- Outils Xilinx: Utilisez Vivado ou impact pour le débogage FPGA.

Étape 3: lire les données d'une puce

1. Configurez le logiciel JTAG

- Créez ou chargez un fichier de configuration spécifiant l'adaptateur JTAG et le périphérique cible.

- Exemple pour OpenOCD:

source [find interface/jlink.cfg] transport select jtag source [find target/stm32f4x.cfg] init halt

- Exemple pour OpenOCD:

2. Détecter le dispositif cible

Exécutez une commande pour scanner la chaîne JTAG et identifier les appareils connectés.

- Pour OpenOCD:

Recherchez des périphériques détectés dans le journal de sortie.openocd -f interface/jlink.cfg -f target/stm32f4x.cfg

3. Dump contenu de la mémoire

Utilisez les commandes JTAG pour lire les régions de mémoire:

- Pour OpenOCD:

dump_image memory.bin 0x08000000 0x10000-

memory.bin: Fichier pour enregistrer le vidage de mémoire. -

0x08000000: Adresse de démarrage. -

0x10000: Nombre d'octets à lire.

-

4. Effectuer des analyses de limite

Les analyses de limite vérifient la connectivité et les fonctionnalités des broches IC.

- Utilisez URJTAG ou OpenOCD pour effectuer des analyses de limite.

- Exemple dans Urjtag:

cable jtagkey detect bsdl path/to/bsdl/file.bsd svf boundary_scan.svf

Étape 4: meilleures pratiques pour le débogage de JTAG

- Sécuriser la connexion: Utilisez des fils courts et fiables pour minimiser le bruit.

- Vérifiez la broche: Vérifiez les connexions de la broche JTAG pour éviter d'endommager l'appareil.

- Firmware de sauvegarde: Sauvegardez toujours le firmware d'origine avant d'apporter des modifications.

- Utilisez un logiciel correct: Assurez-vous que l'outil que vous utilisez prend en charge le périphérique cible.

- Tension de moniteur: Assurez-vous que le périphérique cible fonctionne au niveau de tension correct.

Applications de JTAG

- Débogage du micrologiciel et des logiciels

- Clignoter un nouveau firmware ou des chargeurs de démarrage

- Extraction des données de la mémoire pour analyse

- Diagnostic de défauts de fabrication de PCB

- Matériel ingénieur inversé

Dépannage

-

Dispositif non détecté:

- Vérifiez le câblage et la broche.

- Assurez-vous que l'appareil cible est allumé.

- Vérifiez les niveaux de tension pour la compatibilité.

-

Erreurs JTAG:

- Assurez-vous que le fichier de configuration correct est utilisé.

- Essayez de réduire la vitesse de l'horloge JTAG si la communication échoue.

-

Problèmes d'autorisation:

- Sur Linux, assurez-vous d'avoir des autorisations appropriées pour accéder aux appareils USB (utiliser

sudoou configurerudevrègles).

- Sur Linux, assurez-vous d'avoir des autorisations appropriées pour accéder aux appareils USB (utiliser

Conclusion

JTAG est un outil inestimable pour le débogage et la programmation des puces à un niveau bas. En comprenant les bases du matériel et des logiciels JTAG, vous pouvez lire la mémoire des puces, déboguer le micrologiciel et effectuer des analyses de limite. Expérimentez avec différents outils et configurations pour utiliser pleinement JTAG dans vos projets!