JTAG (Gruppo di azione di prova articolare) è un protocollo ampiamente utilizzato per il debug, la programmazione e il test di circuiti integrati (ICS). Consente alla comunicazione diretta con un chip di leggere la sua memoria, eseguire scansioni limite o caricare il firmware. Questo tutorial ti guiderà attraverso le basi dell'utilizzo di JTAG per leggere i chip, inclusi configurazione, strumenti e migliori pratiche.

Cos'è JTAG?

JTAG è un'interfaccia standardizzata (IEEE 1149.1) che fornisce un modo per testare e debug hardware a livello di chip. È comunemente usato in:

- Sviluppo e debug del firmware

- Test di connessioni PCB

- Firmware lampeggiante sui dispositivi

- Estrarre la memoria da ICS

JTAG utilizza un'interfaccia a 4 o 5 pin:

| Spillo | Descrizione |

|---|---|

| Tdi | Test dei dati in |

| Tdo | Testare i dati |

| TCK | Orologio di prova |

| TMS | Modalità test Seleziona |

| Trst | Test Reset (opzionale) |

Cosa avrai bisogno

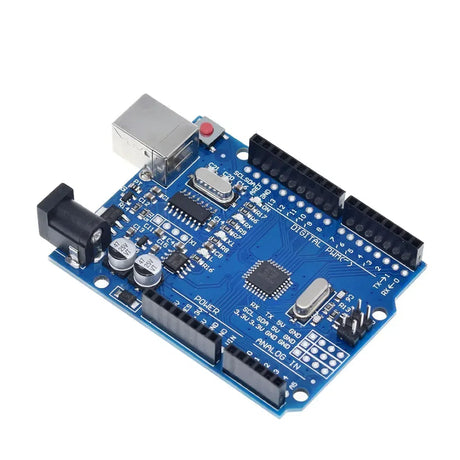

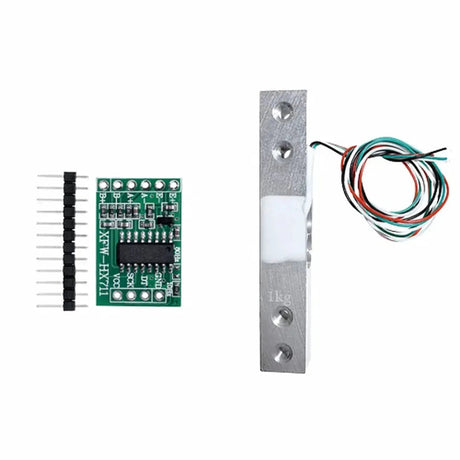

- Adattatore JTAG: Un dispositivo hardware per interfacciarsi con il chip (ad es. Segger J-Link, adattatori supportati da OpenOCD).

- Dispositivo target: IC o sistema che desideri leggere.

- Strumenti software: Applicazioni per il debug JTAG, come OpenOCD, URJtag o strumenti proprietari.

- Documentazione di pinout JTAG: Diagramma di pinout per il dispositivo target.

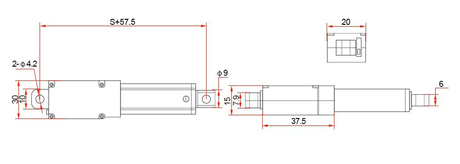

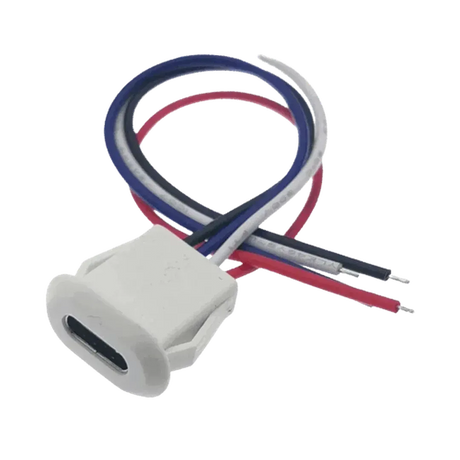

- Accessori di connessione: Fili, intestazioni e una breadboard (se necessario).

Passaggio 1: impostare l'hardware JTAG

1. Identificare l'interfaccia JTAG sul dispositivo di destinazione

- Fare riferimento al foglio dati del chip o agli schemi PCB per individuare i pin JTAG.

- Le etichette comuni per i pin Jtag includono

TDI,TDO,TCK, ETMS. - Alcune schede hanno etichettato le intestazioni JTAG (ad es. Connettori a 10 pin o 20 pin).

2. Collegare l'adattatore JTAG

- Filare l'adattatore al dispositivo target, corrispondente al pinout JTAG:

-

TDISull'adattatore si collegaTDISul dispositivo e così via. - Assicurarsi che GND sia collegato tra l'adattatore e il bersaglio.

- Fornire energia al dispositivo target, se necessario.

-

3. Verifica i livelli di tensione

- Assicurarsi che l'adattatore JTAG supporti i livelli di tensione del dispositivo target (ad es. 3,3 V o 1,8 V).

- Alcuni adattatori hanno impostazioni di tensione configurabili.

Passaggio 2: installazione di strumenti software JTAG

1. OpenOCD (Debugger Open On-Chip)

OpenOCD è uno strumento open source ampiamente utilizzato per il debug JTAG.

- Installalo utilizzando il tuo gestore pacchetti (ad es.

apt install openocdsu Linux). - Assicurati che il tuo adattatore JTAG sia supportato da OpenOCD.

2. Urjtag

Uno strumento leggero per la scansione dei confini e le operazioni JTAG di base.

- Installa via Sito web di Urjtag.

3. Strumenti specifici del fornitore

Per gli adattatori proprietari come Segger J-Link o Xilinx, utilizzare il loro software ufficiale:

- Segger J-Link: Scarica gli strumenti J-Link da Il sito web di Segger.

- Strumenti Xilinx: Usa Vivado o Impact per il debug FPGA.

Passaggio 3: leggere i dati da un chip

1. Configurare il software JTAG

- Creare o caricare un file di configurazione che specifica l'adattatore JTAG e il dispositivo target.

- Esempio per openocd:

source [find interface/jlink.cfg] transport select jtag source [find target/stm32f4x.cfg] init halt

- Esempio per openocd:

2. Rileva il dispositivo di destinazione

Esegui un comando per scansionare la catena JTAG e identificare i dispositivi connessi.

- Per openocd:

Cerca dispositivi rilevati nel registro di output.openocd -f interface/jlink.cfg -f target/stm32f4x.cfg

3. Dump Memory Content

Usa i comandi JTAG per leggere le regioni di memoria:

- Per openocd:

dump_image memory.bin 0x08000000 0x10000-

memory.bin: File per salvare il dump di memoria. -

0x08000000: Inizia l'indirizzo. -

0x10000: Numero di byte da leggere.

-

4. Esegui scansioni di confine

Le scansioni dei confini verificano la connettività e la funzionalità dei pin IC.

- Usa URJtag o OpenOCD per eseguire scansioni di confine.

- Esempio in urjtag:

cable jtagkey detect bsdl path/to/bsdl/file.bsd svf boundary_scan.svf

Passaggio 4: best practice per il debug JTAG

- Proteggere la connessione: Utilizzare fili corti e affidabili per ridurre al minimo il rumore.

- Verifica il pinout: Controllare doppio le connessioni del pin jtag per evitare di danneggiare il dispositivo.

- Firmware di backup: Esegui sempre il backup del firmware originale prima di apportare modifiche.

- Usa il software corretto: Assicurati che lo strumento che stai utilizzando supporti il dispositivo target.

- Monitor Tensione: Assicurarsi che il dispositivo target funzioni a livello di tensione corretto.

Applicazioni di JTAG

- Debug di firmware e software

- Lampeggiare nuovi firmware o bootloader

- Estrarre dati dalla memoria per l'analisi

- Diagnosi di difetti di produzione di PCB

- Hardware di ingegneria inversa

Risoluzione dei problemi

-

Dispositivo non rilevato:

- Verifica il cablaggio e il pinout.

- Assicurarsi che il dispositivo target sia acceso.

- Controllare i livelli di tensione per la compatibilità.

-

Errori JTAG:

- Assicurarsi che venga utilizzato il file di configurazione corretto.

- Prova a ridurre la velocità di clock JTAG se la comunicazione fallisce.

-

Problemi di autorizzazione:

- Su Linux, assicurati di avere autorizzazioni adeguate per accedere ai dispositivi USB (utilizzo

sudoo configurareudevregole).

- Su Linux, assicurati di avere autorizzazioni adeguate per accedere ai dispositivi USB (utilizzo

Conclusione

JTAG è uno strumento inestimabile per i chip di debug e di programmazione a basso livello. Comprendendo le basi dell'hardware e del software JTAG, è possibile leggere la memoria dei chip, il firmware del debug ed eseguire scansioni di confine. Sperimenta diversi strumenti e configurazioni per utilizzare pienamente JTAG nei tuoi progetti!