JTAG (wspólna grupa akcji testowej) jest szeroko stosowanym protokołem do debugowania, programowania i testowania obwodów zintegrowanych (ICS). Umożliwia bezpośrednią komunikację z układem w celu odczytu jego pamięci, wykonywania skanów granicznych lub ładowania oprogramowania układowego. Ten samouczek poprowadzi Cię podstawy używania JTAG do czytania układów, w tym konfiguracji, narzędzi i najlepszych praktyk.

Co to jest JTAG?

JTAG to znormalizowany interfejs (IEEE 1149.1), który zapewnia sposób testowania i debugowania sprzętu na poziomie układu. Jest powszechnie używany w:

- Rozwój i debugowanie oprogramowania

- Testowanie połączeń PCB

- Miganie oprogramowania na urządzeniach

- Wyodrębnienie pamięci z ICS

JTAG używa interfejsu 4 lub 5-styków:

| Szpilka | Opis |

|---|---|

| TDI | Dane testowe w |

| TDO | Przetestuj dane |

| Tck | Zegar testowy |

| TMS | Tryb testowy Wybierz |

| Trst | Reset testu (opcjonalnie) |

Czego będziesz potrzebować

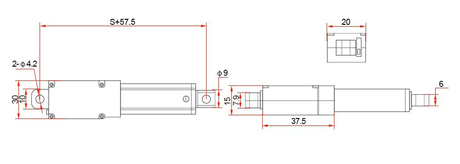

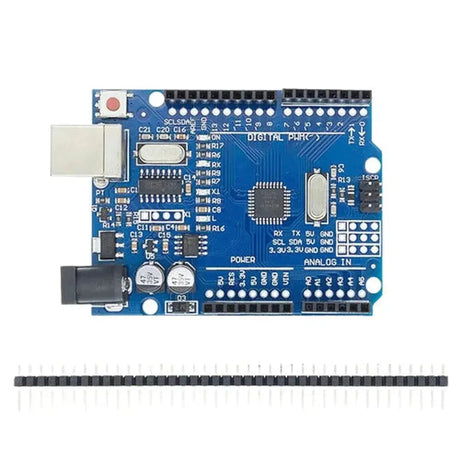

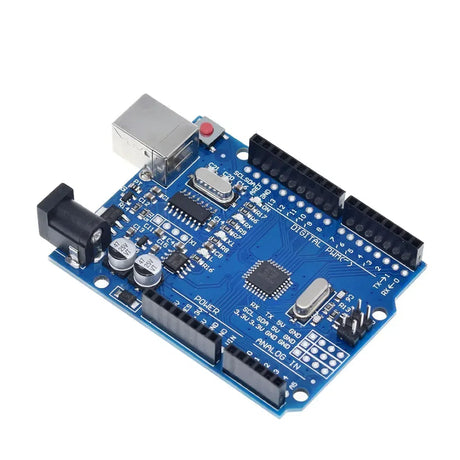

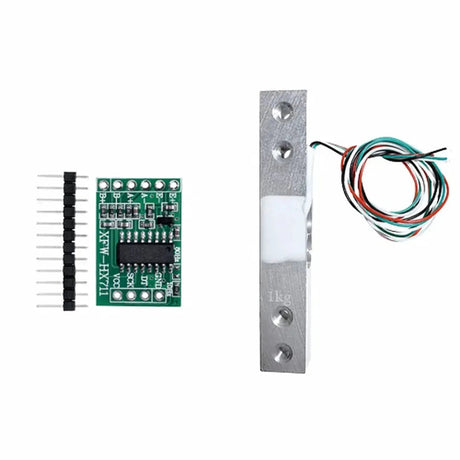

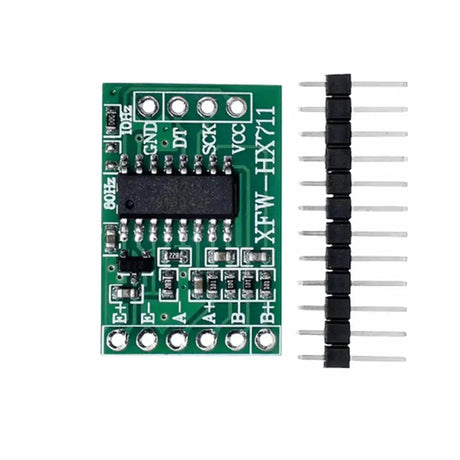

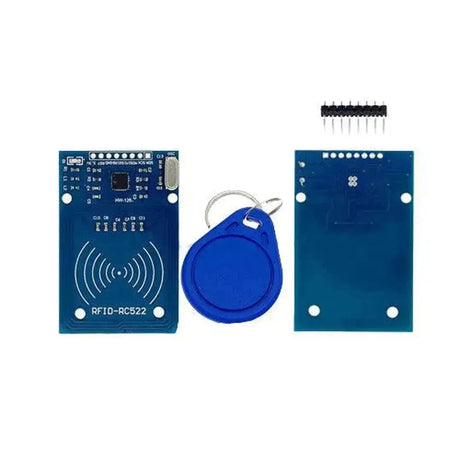

- Adapter JTAG: Urządzenie sprzętowe do interfejsu z układem (np. Segger J-Link, adaptery wspierane przez OpenOCD).

- Urządzenie docelowe: IC lub system, który chcesz przeczytać.

- Narzędzia programowe: Aplikacje do debugowania JTAG, takie jak narzędzia OpenOCD, URJTAG lub zastrzeżone.

- Dokumentacja pinout JTAG: Schemat pinout dla urządzenia docelowego.

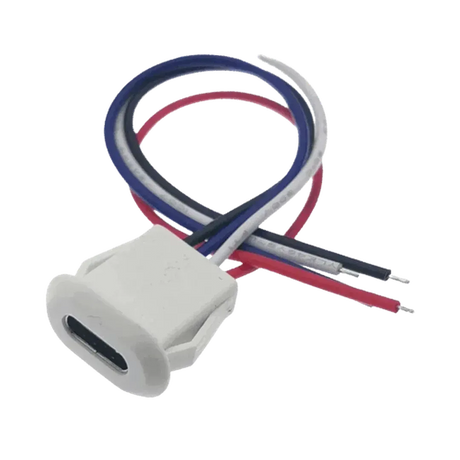

- Akcesoria do połączeń: Przewody, nagłówki i płyta chlebowa (w razie potrzeby).

Krok 1: Konfigurowanie sprzętu JTAG

1. Zidentyfikuj interfejs JTAG na urządzeniu docelowym

- Zapoznaj się z arkuszem danych lub schematów PCB, aby zlokalizować szpilki JTAG.

- Wspólne etykiety dla pinów JTAG obejmują

TDI,TDO,TCK, ITMS. - Niektóre tablice oznaczono nagłówki JTAG (np. 10-pinowe lub 20-pinowe złącza).

2. Podłącz adapter JTAG

- Podłączyć adapter do urządzenia docelowego, dopasowując pinout JTAG:

-

TDIna adapterze łączy się zTDIna urządzeniu i tak dalej. - Upewnij się, że GND jest połączony między adapterem a celem.

- W razie potrzeby zapewnij zasilanie urządzeniu docelowym.

-

3. Sprawdź poziomy napięcia

- Upewnij się, że adapter JTAG obsługuje poziomy napięcia urządzenia docelowego (np. 3,3 V lub 1,8 V).

- Niektóre adaptery mają konfigurowalne ustawienia napięcia.

Krok 2: Instalowanie narzędzi oprogramowania JTAG

1. OpenOCD (otwarty debugger na chipie)

OpenOCD to narzędzie open source, powszechnie używane do debugowania JTAG.

- Zainstaluj go za pomocą menedżera pakietów (np.

apt install openocdna Linux). - Upewnij się, że adapter JTAG jest obsługiwany przez OpenOCD.

2. Urjtag

Lekkie narzędzie do skanowania granicznego i podstawowych operacji JTAG.

- Zainstaluj Witryna URJTAG.

3. Narzędzia specyficzne dla dostawcy

W przypadku zastrzeżonych adapterów, takich jak Segger J-Link lub Xilinx, użyj ich oficjalnego oprogramowania:

- Segger J-Link: Pobierz narzędzia J-Link z Witryna Seggera.

- Narzędzia xilinx: Użyj Vivado lub wpływ na debugowanie FPGA.

Krok 3: Odczyt danych z układu

1. Skonfiguruj oprogramowanie JTAG

- Utwórz lub załaduj plik konfiguracyjny określający adapter JTAG i urządzenie docelowe.

- Przykład dla OpenOCD:

source [find interface/jlink.cfg] transport select jtag source [find target/stm32f4x.cfg] init halt

- Przykład dla OpenOCD:

2. Wykryj urządzenie docelowe

Uruchom polecenie, aby zeskanować łańcuch JTAG i zidentyfikować podłączone urządzenia.

- Dla OpenOCD:

Poszukaj wykrytych urządzeń w dzienniku wyjściowym.openocd -f interface/jlink.cfg -f target/stm32f4x.cfg

3. Zrzucanie zawartości pamięci

Użyj poleceń JTAG, aby odczytać regiony pamięci:

- Dla OpenOCD:

dump_image memory.bin 0x08000000 0x10000-

memory.bin: Plik, aby zapisać zrzut pamięci. -

0x08000000: Rozpocznij adres. -

0x10000: Liczba bajtów do przeczytania.

-

4. Wykonaj skany graniczne

Skany graniczne sprawdzają łączność i funkcjonalność pinów IC.

- Użyj URJTAG lub OpenOCD do wykonywania skanów granicznych.

- Przykład w urjtag:

cable jtagkey detect bsdl path/to/bsdl/file.bsd svf boundary_scan.svf

Krok 4: Najlepsze praktyki debugowania JTAG

- Zabezpiecz połączenie: Użyj krótkich, niezawodnych przewodów, aby zminimalizować szum.

- Sprawdź pinout: Dokładnie sprawdź połączenia PIN JTAG, aby uniknąć uszkodzenia urządzenia.

- Tworzenie kopii zapasowych oprogramowania: Zawsze wykonaj kopię zapasową oryginalnego oprogramowania układowego przed wprowadzeniem zmian.

- Użyj poprawnego oprogramowania: Upewnij się, że narzędzie, którego używasz, obsługuje urządzenie docelowe.

- Monitorowanie napięcia: Upewnij się, że urządzenie docelowe działa we właściwym poziomie napięcia.

Zastosowania JTAG

- Debugowanie oprogramowania i oprogramowania

- Miga nowe oprogramowanie układowe lub ładowarki

- Wyodrębnienie danych z pamięci do analizy

- Diagnozowanie wad produkcyjnych PCB

- Sprzęt do inżynierii odwrotnej

Rozwiązywanie problemów

-

Urządzenie nie wykryte:

- Sprawdź okablowanie i pinout.

- Upewnij się, że urządzenie docelowe jest włączone.

- Sprawdź poziomy napięcia pod kątem zgodności.

-

Błędy JTAG:

- Upewnij się, że używany jest prawidłowy plik konfiguracyjny.

- Spróbuj obniżyć prędkość zegara JTAG, jeśli komunikacja się nie powiedzie.

-

Problemy z uprawnieniami:

- W systemie Linux upewnij się, że masz odpowiednie uprawnienia do dostępu do urządzeń USB (używaj

sudolub skonfigurujudevzasady).

- W systemie Linux upewnij się, że masz odpowiednie uprawnienia do dostępu do urządzeń USB (używaj

Wniosek

JTAG jest nieocenionym narzędziem do debugowania i programowania układów na niskim poziomie. Rozumiejąc podstawy sprzętu i oprogramowania JTAG, możesz odczytać pamięć układu, debugować oprogramowanie układowe i wykonywać skany graniczne. Eksperymentuj z różnymi narzędziami i konfiguracją, aby w pełni wykorzystać JTAG w swoich projektach!