O JTAG (Grupo de Ação de Teste Conjunto) é um protocolo amplamente utilizado para depuração, programação e teste de circuitos integrados (ICS). Ele permite que a comunicação direta com um chip leia sua memória, execute verificações de limite ou o firmware de carga. Este tutorial o guiará através do básico do uso do JTAG para ler chips, incluindo configuração, ferramentas e práticas recomendadas.

O que é JTAG?

O JTAG é uma interface padronizada (IEEE 1149.1) que fornece uma maneira de testar e depurar hardware no nível do chip. É comumente usado em:

- Desenvolvimento de firmware e depuração

- Testando conexões de PCB

- Firmware piscando em dispositivos

- Extraindo a memória do ICS

O JTAG usa uma interface de 4 ou 5 pinos:

| Alfinete | Descrição |

|---|---|

| TDI | Dados de teste em |

| Tdo | Dados de teste fora |

| Tck | Relógio de teste |

| Tms | Modo de teste Selecione |

| Trst | Redefinição de teste (opcional) |

O que você precisará

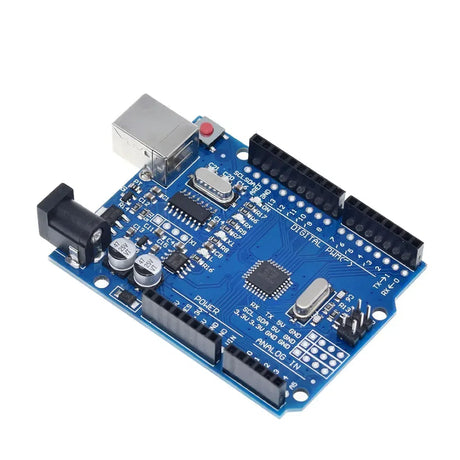

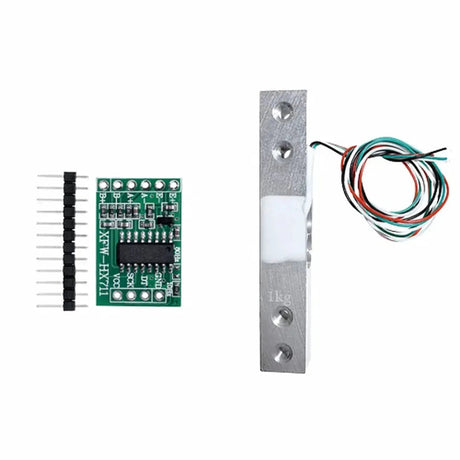

- Adaptador JTAG: Um dispositivo de hardware para interagir com o chip (por exemplo, segger j-link, adaptadores apoiados pelo OpenocD).

- Dispositivo de destino: O IC ou sistema que você deseja ler.

- Ferramentas de software: Aplicativos para depuração JTAG, como Ferramentas Openocd, UrjTag ou Proprietário.

- Documentação do pinout jTAG: Diagrama de pinagem para o dispositivo de destino.

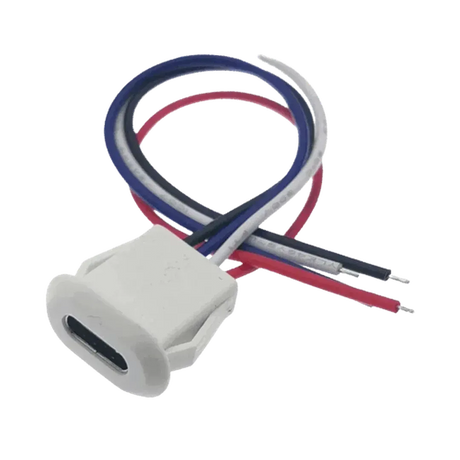

- Acessórios de conexão: Fios, cabeçalhos e uma placa de ensaio (se necessário).

Etapa 1: Configurando o hardware JTAG

1. Identifique a interface JTAG no dispositivo de destino

- Consulte a folha de dados do chip ou os esquemas da PCB para localizar os pinos JTAG.

- Etiquetas comuns para pinos JTAG incluem

TDI,TDO,TCK, eTMS. - Algumas placas rotularam cabeçalhos JTAG (por exemplo, conectores de 10 ou 20 pinos).

2. Conecte o adaptador JTAG

- Ajude o adaptador ao dispositivo de destino, correspondendo à pinagem de JTAG:

-

TDIno adaptador se conecta aTDIno dispositivo, e assim por diante. - Verifique se o GND está conectado entre o adaptador e o alvo.

- Forneça energia ao dispositivo de destino, se necessário.

-

3. Verifique os níveis de tensão

- Verifique se o adaptador JTAG suporta os níveis de tensão do dispositivo de destino (por exemplo, 3,3V ou 1.8V).

- Alguns adaptadores têm configurações de tensão configuráveis.

Etapa 2: Instalando ferramentas de software JTAG

1. Openocd (Open On Chip Debugger)

O Openocd é uma ferramenta de código aberto amplamente utilizado para a depuração do JTAG.

- Instale -o usando seu gerenciador de pacotes (por exemplo,

apt install openocdno Linux). - Verifique se o seu adaptador JTAG é suportado pelo Openocd.

2. Urjtag

Uma ferramenta leve para varredura de limite e operações básicas de JTAG.

- Instale via Site de Urjtag.

3. Ferramentas específicas do fornecedor

Para adaptadores proprietários como Segger J-Link ou Xilinx, use seu software oficial:

- Segger J-Link: Baixe as ferramentas J-Link de Site de Segger.

- Ferramentas Xilinx: Use Vivado ou impacto para a depuração do FPGA.

Etapa 3: Lendo dados de um chip

1. Configure o software JTAG

- Crie ou carregue um arquivo de configuração especificando o adaptador JTAG e o dispositivo de destino.

- Exemplo para Openocd:

source [find interface/jlink.cfg] transport select jtag source [find target/stm32f4x.cfg] init halt

- Exemplo para Openocd:

2. Detecte o dispositivo alvo

Execute um comando para digitalizar a cadeia JTAG e identificar dispositivos conectados.

- Para openocd:

Procure dispositivos detectados no log de saída.openocd -f interface/jlink.cfg -f target/stm32f4x.cfg

3. Despeno de conteúdo da memória

Use comandos JTAG para ler regiões de memória:

- Para openocd:

dump_image memory.bin 0x08000000 0x10000-

memory.bin: Arquivo para salvar o despejo de memória. -

0x08000000: Iniciar o endereço. -

0x10000: Número de bytes para ler.

-

4. Realize varreduras de limite

As varreduras de limite verificam a conectividade e a funcionalidade dos pinos do IC.

- Use UrjTag ou Openocd para realizar varreduras de limite.

- Exemplo em urjtag:

cable jtagkey detect bsdl path/to/bsdl/file.bsd svf boundary_scan.svf

Etapa 4: práticas recomendadas para depuração JTAG

- Prenda a conexão: Use fios curtos e confiáveis para minimizar o ruído.

- Verifique a pinout: Verifique duas conexões de pino JTAG para evitar danificar o dispositivo.

- Firmware de backup: Sempre faça backup do firmware original antes de fazer alterações.

- Use o software correto: Verifique se a ferramenta que você está usando suporta o dispositivo de destino.

- Monitore a tensão: Verifique se o dispositivo de destino opera no nível de tensão correto.

Aplicações do JTAG

- Firmware e software de depuração

- Piscando novos firmware ou carregadores de inicialização

- Extraindo dados da memória para análise

- Diagnóstico de defeitos de fabricação de PCBs

- Hardware de engenharia reversa

Solução de problemas

-

Dispositivo não detectado:

- Verifique a fiação e a pinagem.

- Verifique se o dispositivo de destino está ligado.

- Verifique os níveis de tensão para compatibilidade.

-

Erros JTAG:

- Verifique se o arquivo de configuração correto é usado.

- Tente abaixar a velocidade do relógio JTAG se a comunicação falhar.

-

Problemas de permissão:

- No Linux, verifique se você tem permissões adequadas para acessar dispositivos USB (use

sudoou configureudevregras).

- No Linux, verifique se você tem permissões adequadas para acessar dispositivos USB (use

Conclusão

O JTAG é uma ferramenta inestimável para depuração e programação de chips em um nível baixo. Ao entender o básico do hardware e do software JTAG, você pode ler a memória do chip, o firmware de depuração e executar verificações de limites. Experimente diferentes ferramentas e configurações para utilizar totalmente o JTAG em seus projetos!